随着存储容量的不断增长,NAND Flash存储原厂的产品生产工艺也在不断发展,存储晶圆工艺制程、电子单元密度、闪存堆叠层数等都经历了较大的技术迭代和发展。

为了提升密度,闪存厂商做了哪些努力?

回顾3D NAND闪存的发展历程,东芝最早在2007年提出了此概念,并表明NAND闪存未来的发展趋势将集中于降低单位bit成本。2013年,三星推出了全球首款V-NAND闪存,并投入量产,代表着3D NAND闪存从技术概念走向了商业市场。三星第一代V-NAND闪存采用了三星电子独创圆柱形3D CTF和垂直堆叠技术,虽然只有24层,但却突破了平面技术的瓶颈。反观东芝,其第一款3D NAND(48层)量产产品比三星晚了整整三年。

有数据统计,2019年,3D NAND的渗透率为72.6%,已远超2D NAND,且未来仍将持续提高,预计2025年3D NAND 将占闪存总市场的97.5%。

自从NAND闪存进入3D时代,芯片的层数比拼一直是各大NAND闪存芯片厂商竞争的重点,堆栈层数犹如摩天大楼一样越来越高。在3D NAND技术赛跑中,存储厂商从最初的24层、32层,一路堆到了128层、176层,甚至200+层。层数越高,NAND闪存可具有的容量就越大,增加层数以及提高产量也是衡量技术实力的标准。

前不久,美光宣布其232层NAND闪存芯片实现量产,这也是全球首款突破200层大关的固态存储芯片。

芯片制程“双刃剑”

此外,NAND的制程是另一个影响NAND存储密度的关键因素。2D NAND从早期50+nm到19nm,最后发展到了16/15nm,每次制程的升级都将NAND存储密度提升到新的高度,但是NAND闪存的制程工艺是双刃剑,容量提升、成本降低的同时可靠性及性能都在下降,因为工艺越先进,NAND的氧化层越薄,可靠性也越差,厂商就需要采取额外的手段来弥补,但这又会提高成本,以致于达到某个点之后制程工艺已经无法带来优势了。从TechInsights闪存路线图中获悉,2D NAND闪存以工艺制程演进为评判标准,而迈入3D NAND之后,工艺制程演进相对缓慢,堆叠层数取代工艺制程成为新的介质进化标准。

从各厂商的技术蓝图来看,NAND Flash堆叠层数预计在2022年将达到2XX层,而工艺制程则可能停留在20nm左右。

写在最后

NAND闪存的概念可以追溯到上世纪80年代,而真正步入发展轨道则是从2000年开始。从WSTS公布的出货量数据来看,NAND闪存的发展大致可以分为三个阶段。2000年至2016年间,NAND闪存出货量呈现线性增长趋势;2016年至2018年,出货量相对稳定;2018年之后,受益于数据中心市场增长,NAND闪存出货量随之增加。

从NAND闪存市场的角度看,随着2001年以后音乐播放器、数码相机、手机等领域疾速增长,NAND闪存市场需求持续上扬,出货量以线性趋势持续增加

在 NAND闪存扩展饱和后,随着大数据、物联网、数据中心等新兴市场的发展,三星、英特尔、铠侠、西部数据、长江存储等一系列闪存厂商再次纷纷加速技术演进和市场布局,以争夺NAND闪存市场的主导权。

医用导管等离子清洗机 PLAUX-PT1800

医用导管等离子清洗机 PLAUX-PT1800 【普乐斯】卷对卷低温等离子表面处理机

【普乐斯】卷对卷低温等离子表面处理机 【普乐斯】EPDM低温等离子表面处理机-PG-1000ZE

【普乐斯】EPDM低温等离子表面处理机-PG-1000ZE 真空等离子清洗机报警灯

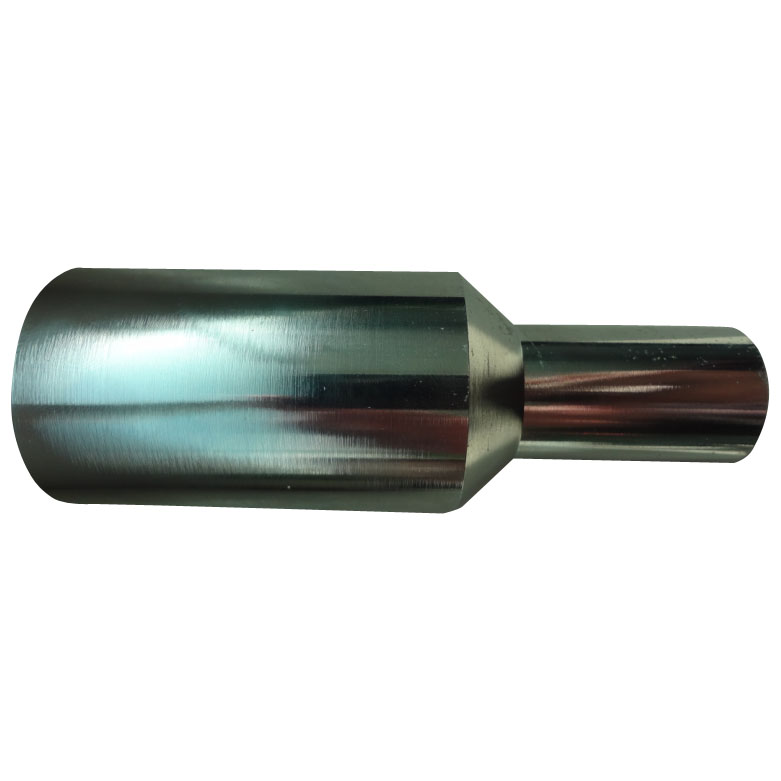

真空等离子清洗机报警灯 射流等离子清洗机外壳

射流等离子清洗机外壳 【普乐斯】准辉光实验大气等离子清洗机PLAUX-CTP-2000

【普乐斯】准辉光实验大气等离子清洗机PLAUX-CTP-2000 【普乐斯】桌上型真空等离子清洗机-PMT-100

【普乐斯】桌上型真空等离子清洗机-PMT-100 【普乐斯】等离子清洗机仪器PM/R-T5LN01

【普乐斯】等离子清洗机仪器PM/R-T5LN01 【普乐斯】射流大气等离子体清洗机设备-SZ-300

【普乐斯】射流大气等离子体清洗机设备-SZ-300 【普乐斯】半导体真空等离子清洗机设备 VPC-500F8

【普乐斯】半导体真空等离子清洗机设备 VPC-500F8